Завершено развитие платформы RISC-V MEEP для будущих европейских суперкомпьютеров

Дата: 26.09.2023 03:21

Игры в разработке

Европейский союз продолжает активно разрабатывать собственное видение суперкомпьютеров в ближайшем будущем, которые будут основаны на архитектуре RISC-V. За три с половиной года работы проект Marenostrum Experimental Exascale Platform (MEEP) создал новую платформу, подробно описывающую различные блоки и свойства таких HPC-систем.

Выбор микроархитектуры RISC-V в качестве основы MEEP вполне обоснован - она открыта и позволяет разработчикам не зависеть от собственных наборов команд и аппаратных решений. Таким образом, ЕС планирует достичь автономии в области суперкомпьютеров, приобретая собственную платформу.

На стадии разработки MEEP лежит ускоренный механизм памяти и вычислений (ACME), который изначально разрабатывался для использования высокоскоростной памяти HBM3 и состоит из Memory Tile и VAS вычислительных блоков, соединенных сетью меш-интерконнект. Перевести дизайн ACME в реальный силикон - вопрос еще будущего, но уже ясно, что процессоры, разработанные в рамках проекта MEEP, будут иметь структуру чиплета.

В дизайне ACME Memory Tile обрабатывает все операции с подсистемами памяти, включая построение иерархических массивов с использованием различных типов памяти, включая MRAM и HBM3. Модули VAS включают 8 ядер процессора, каждое из которых имеет собственные секции кеша L2. Каждое такое ядро состоит из нескольких отдельных блоков: скалярного RISC-V, блока векторных операций, а также блоков ускорителей двух типов - SA-HEVC для обработки видео и SA-NN для задач нейронных сетей, в частности, вывода.

На самом деле каждый модуль VAS - это полностью самостоятельный многоядерный процессор RISC-V, способный работать с современными форматами данных, автоматически распознавать продвинутые инструкции и выполнять их с использованием соответствующих ускорителей в своем составе.

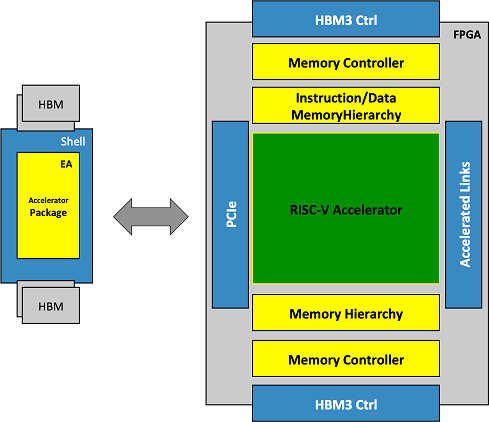

Платформа, созданная в рамках проекта MEEP, уже функционирует как полноценный прототип, эмулируемый с использованием FPGA от Xilinx. Она позволяет не только разрабатывать и отлаживать программное обеспечение для новой европейской суперкомпьютерной экосистемы, но и валидировать аппаратные компоненты для будущих ускорителей/процессоров с архитектурой ACME.